International Journal of Research Studies in Electrical and Electronics Engineering (IJRSEEE)

Volume 3, Issue 4, 2017, PP 1-4

ISSN 2454-9436 (Online)

DOI: http://dx.doi.org/10.20431/2454-9436.0304001

www.arcjournals.org

# Design of Frequency Meter Unit for Low-Power Integrated Circuits

Artyom O. Popov<sup>1</sup>, Alexander S. Sinyukin<sup>2</sup>

<sup>1</sup> BSc of Southern Federal University, Russia, 44, Nekrasovsky lane, Taganrog, 347928, Russia

<sup>2</sup> MSc of Southern Federal University, Russia, 44, Nekrasovsky lane, Taganrog, 347928, Russia

\*Corresponding Author: Alexander S. Sinyukin, MSc of Southern Federal University, Russia, 44, Nekrasovsky lane, Taganrog, 347928, Russia

**Abstract:** The development of a circuit and layout of the frequency meter unit for low-power integrated circuits is represented in this article. Simulation results of the device for 90 nm CMOS technology are considered. An estimation of a range of the measurable frequencies for certain values of counter stages at clock frequencies 0.25, 0.5, 1 GHz was carried out. Besides, dependences of power consumption on the frequency of the clock oscillator at the measurable frequencies from 10 MHz to 50 MHz were obtained.

Keywords: digital frequency meter, low-power integrated circuits, CMOS VLSI, circuit simulation

## **1. INTRODUCTION**

With rising of integration level of VLSI circuits, requirements to the power consumption of IC elements are increasing [1]. Consequently there is strong demand for low-power circuits. This is especially important for mobile devices with wireless power supply: RFID applications, micro-robots, implantable diagnostic chips, biomedical applications, wireless detection of environmental parameters, navigation. In particular, capacitive sensors, e.g. accelerometers or gyroscopes, require low-power capacitance-to-digital converters [2]. The unit for the frequency measurement with subsequent conversion of the frequency to binary code is considered in this article. The device was designed for implementation in CMOS technology with 90 nm design rules [3].

# 2. OPERATING PRINCIPLE AND DESIGN OF THE PROPOSED DIGITAL FREQUENCY METER

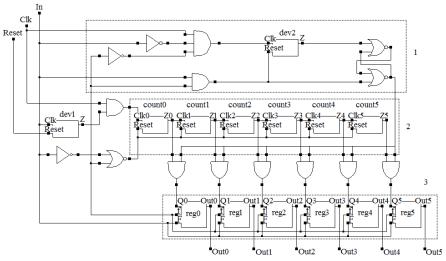

A circuit of the frequency meter for the low-power systems, designed using logic editor and simulator DSCH [4], is shown in Figure 1. There are three dotted areas in the figure: 1 - driver of the write delay from the counter to the register, 2 - n-stage counter, 3 - n-stage parallel register.

**Figure1.** Schematic circuit of the frequency meter unit: 1 - delay driver; 2 - n-stage counter; 3 - n-stage parallel register

After a short positive pulse has been applied to 'Reset' 'input, during applying the measurable signal with F frequency to 'In' input, signal with frequency

$$f = \frac{F}{2} \tag{1}$$

is appearing at output 'Z' of the single-order counter dev1. This enables to measure the signal frequency F during its period

$$T_F = \frac{1}{F} \tag{2}$$

At rise edge of the signal f, the signal *Clk*, whose frequency is much more than the frequency f, flows to 'Clk' input of the *n*-stage counter. Number of clock pulses corresponding to certain binary code arises at outputs of the counter. This binary code is transmitted to parallel register (area 3 in Figure 1) after the delay formed by delay driver (area 1 in Figure 1) and stored during time

$$t = 1.5 \cdot T_F. \tag{3}$$

In this way, the parallel register stores previous state of the *n*-stage counter while the counter performs next measurement. The driver of the write delay from the counter to the register is necessary to prevent concurrence uncertainty, which would appear during transitions of the *n*-stage counter from one state to another. Cell AND3 passes *Clk* signal to the input of *n*-stage counter at the fall edges of signals F and f and it passes *Reset* signal at the rise edges of these signals. Reset of *n*-stage counter to zero takes place when the rise edge of F signal and the fall edge of f signal are simultaneously applied. Reset of the parallel register to zero occurs when the rise edges both of F signal and f signal are simultaneously applied.

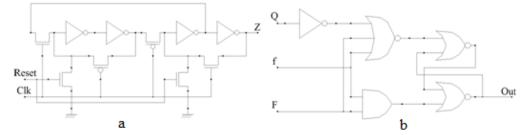

**Figure2.** Schematics of the cells: a - schematic of single-order counter [1]; <math>b - schematic of the parallel register cell

In Figure 2a schematic of single-order counter is shown [1] and schematic of the developed parallel register cell is shown in Figure 2b.

Minimum frequency value, which can be measured by this frequency meter, depends on clock frequency  $F_{\text{Clk}}$  and the number *n* of the counter stages. Maximum measurable frequency is limited by high-order bit of the *n*-stage counter and it also depends on proper operation of the delay driver.

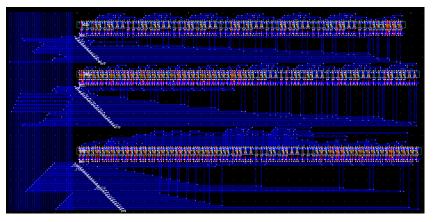

The layout of the frequency meter unit created using Microwind software tools [4] for 90 nm CMOS technology is shown in Figure 3. The total area occupied by the frequency meter on the chip is about  $4077 \ \mu\text{m}^2$ .

Figure3. Layout of the frequency meter unit

International Journal of Research Studies in Electrical and Electronics Engineering (IJRSEEE) Page | 2

#### 3. SIMULATION AND DISCUSSION

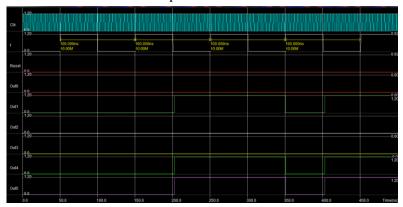

The simulation of the frequency meters was conducted using Microwind for number of stages n = 10, clock frequency  $F_{\text{Clk}} = 0.5$  GHz and measurable frequency F = 10 MHz. The results of the simulation are shown in Figure 4. The timing diagrams showed in the Figure 4 completely corresponds to the operating principle of the device described in previous section.

Figure4. Simulation of the frequency meter for 6-stage counter and clock frequency 0.5 GHz

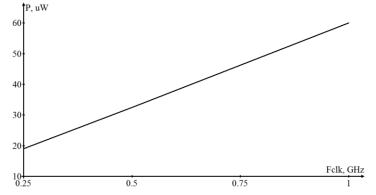

Figure 5 shows dependency of power consumption *P* of frequency meter on the clock oscillator frequency  $F_{\text{Clk}}$  at the measurable frequency F = 10 MHz.

Figure5. Dependence of power consumption on clock frequency at measurable frequency 10 MHz

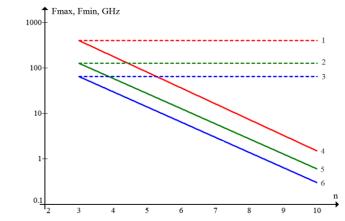

Dependences of minimal  $F_{\min}$  and maximal  $F_{\max}$  measurable frequencies on the number of stages *n* at different clock frequencies are shown in Figure 6. It follows from the figure that with increasing of the number of counter stages *n* the minimum measurable frequency  $F_{\min}$  decreases. This broadens the measuring range of the frequency meter and in addition increases accuracy of the measurement. The increase of clock frequency also enlarges measuring range but leads to significant rising of the power consumption. Therefore choice of number of counter stages *n* and clock frequency  $F_{\text{Clk}}$  totally depends on requirements to the measurable frequencies range  $F_{\min} - F_{\max}$ .

#### 4. CONCLUSION

The design of frequency meter unit for low-power systems is presented in this work. The schematic circuit, the layout and the simulation results are considered. The dependencies of power consumed by frequency meter on clock oscillator frequency as well as dependencies of the measurable frequencies range on the number of counter stages were obtained. Feature of the proposed frequency meter is opportunity of its implementation in the integrated-circuit form as the component of low-power detectors, micromechanical sensors and other devices in which the conversion of the signal frequency to the binary code corresponding to this signal is required.

#### ACKNOWLEDGMENTS

This work was supported by Southern Federal University, project № VnGr-07/2017-10. Authors would like to thank their scientific adviser, Professor Boris G. Konoplev for his comprehensive assistance during this work.

## REFERENCES

- [1] Sicard E., Bendhia S.D. Basics of CMOS Cell Design. McGraw-Hill, 2007, 427 pp.

- [2] Konoplev B.G., Ryndin E.A. High-sensitive capacitance-to-frequency converter. Patent of Russia № 2602493, September 1, 2015.

- [3] Sicard E., Bendhia S.D. Advanced CMOS Cell Design, 2nd ed. McGraw-Hill, 2007, 364 pp.

- [4] Sicard E. Microwind & DSCH v3.5 Lite User's Manual. Toulouse, France: INSA Toulouse, 2009, 130 pp.

#### **AUTHORS' BIOGRAPHY**

**Artyom O. Popov,** received the BSc degree in Nanotechnology and Microsystems Devices at Southern Federal University, Taganrog, Russia, in 2016. Currently he is graduate student at Southern Federal University. His research interests include development of digital functional units for VLSI circuits.

**Alexander S. Sinyukin,** received the BSc degree in Design engineering and technology of electronic devices at Southern Federal University, Taganrog, Russia, in 2015 and the MSc degree at the same university and the same area of study in 2017. Currently he is postgraduate student at Southern Federal University. His research interests include radiofrequency energy-efficient micro systems with wireless power.

**Citation:** Artyom O. Popov & Alexander S. Sinyukin(2017). Design of Frequency Meter Unit for Low-Power Integrated Circuits, International Journal of Research Studies in Electrical and Electronics Engineering (IJRSEEE), 3(4), pp.1-4, DOI: http://dx.doi.org/10.204 31/2454-9436.0304001.

**Copyright:** © 2017 Artyom O. Popov & Alexander S. Sinyukin. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited