# Some Features of the Transport of Charge Carriers in the Grain Boundaries of Polycrystalline Silicon

# L.O. Olimov

Associate Professor of Andizhan State University, Z.M.Babura

# **B.M. Abdurakhmanov**

Senior Research Fellow Institute of Ionic-plasma and laser technologies, Uzbekistan Academy of Sciences

# F.L. Omonboev

Student Andizhan State University, Z.M.Babura

**Abstract:** We propose and discuss the mechanism of charge transport in polycrystalline silicon wafers with a thickness comparable to the grain size. Determining influence on the transport processes of the carriers during heating of the samples have deep energy levels caused by grain boundaries, and thermal generated carriers as a result of interaction with the recombination centers do not recombine, and are involved in the conduction proposed in the article, the mechanism.

In [1,2], where the transport of charge carriers (CC) in the heated polycrystalline semiconductor structures in terms of their interaction with recombination centers associated with deep impurity states in the grain boundaries (GB) was found an abrupt change in the mobility and carrier concentration, which occurs in the temperature range 300+800 K. as a result, the total concentration of CC, as it turns out, is determined by the concentration of CC trapped recombination centers (RC) caused by impurity states and defects in the GB, the total size of the combined layer which two adjacent grains of the polycrystalline silicon (PS) according to [3] is within ~ 7 nm. Sequential expression of RC at the sample is heated PS energy levels, for example, E~0.15 eV, E~0.17 eV, E~0.3 eV and E~0.36 eV, which is accompanied by an increase in the concentration of CC trapped at these levels, with the total concentration of CC is reduced [1, 2], and the conductivity of GB in the PS material increases [3], and, conversely, a decrease in the carrier concentration captured RC leads to an increase in the total concentration of CC [1, 2], but is accompanied by a reduction in the conductivity of GB [3]. Furthermore, during an abrupt change in the concentration of CC takes place switching current and voltage measured in the heated samples, that is, change in direction of motion of the CC, which occurs in the temperature range of [3], within the areas of GB, that is in quantities of nano-metric sizes. Note that the motion of CC in such amounts may be accompanied by quantum size effects.

This work is similar to [1-6] is also devoted to the analysis of the mechanism of charge transport in the area of the GB, ie, process drift of CC at the RC when the sample is heated PS, but contains two innovations.

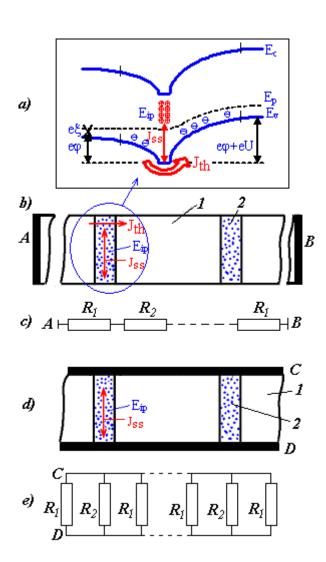

The novelty lies in bringing to explain the processes of transport of CC in the GB (Figure 1a), the thermionic emission model [4] and is selected as the object of study of PS wafers with a thickness comparable to the grain size. Since the samples are selected for the study of PS wafers of p-type conductivity, a thickness of 200 microns and a grain size ~250 microns. The simplified circuit samples embodiment with the contacts on the edges and the planes are shown respectively in Figures 1b and 1d. A figure 1c and 1e shows the equivalent electrical circuit of these options. From Figure 1 it follows that the CC in these samples have transitions of two types, namely, the transition of CC from one grain to another (Figure 1b), and along the GB (ris.1d).

#### L.O. Olimov et al.

Consider the first embodiment the transitions when the ohmic contacts A and B are mounted on the sides of the plate.

Daylight carriers comes from one grain to another, causing seizure is observed, and emission of charge carriers (see Fig. 1a, b). Thus the total current  $J_{th}$  major carriers flowing from left to right can be written as follows [4]:

$$J_{th} = A^* T^2 \exp(\beta(\xi + \varphi)) \left(1 - \exp(\beta U)\right)$$

(1)

Here,  $\beta = e/kT$  - reverse thermal potential difference, e - electron charge, k - Boltzmann constant, T - temperature,  $A^*$  - the effective Richardson constant, U - the applied voltage. Shifted in the forward direction barrier is denoted by  $e\varphi$ , and  $e\xi$  - depending on the concentration of the doping, the Fermi level in the crystal grains.

As shown in Fig. 1a and b, the holes are trapped at the interface states lying above the Fermi level  $E_{ip}$ , ie in the GB. Corresponding positive charge is compensated by a negative infected acceptors in the space charge region. Thermionic emission current creates  $J_{th}$ , the current from left to right. In addition to current  $J_{th}$  at the GB, there is also a second current  $J_{ss}$ , shown in Fig. 1a and b. This current is determined by the difference between  $J_{ss}$  intensities capture and emission holes.  $J_{ss}$  current is:

$$J_{ss} = Y_{ss}\delta\varphi$$

**Fig 1.** Band diagram (a) and the simplified scheme (b and d) polycrystalline structures and their equivalent electrical circuit (c and e). 1 - grainpolysilicon 2 - area of grain boundaries. A, B, C and D - ohmic contacts. R1 and R2, respectively, electrical resistance of grains and grain boundaries.

(2)

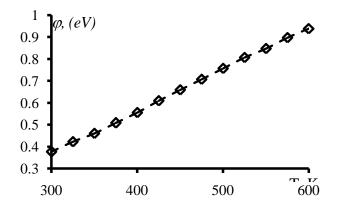

Current  $J_{ss}$  identically equal to the time derivative of the associated interfacial charge. At the GB of the following phenomenon occurs [4] in accordance with the processes of capture and emission of CC at the interface, to maintain full electro neutrality, changing the width of the space charge region. This in its turn affects the entire band diagram (see Fig. 1a) and the change in the barrier height  $e\varphi$ . That is, between the currents  $J_{ss}$  and change the barrier height has  $e\varphi$  feedback. A vibrational property of this feedback is completely determined by the properties of traps, and the link itself arises due to changes in temperature. Using [7, 8] in Figure 2 shows a plot of the potential barrier height of the temperature, an increase in the height of the potential barrier, with the subsequent lowered - the potential barrier height decreases under reduced dependence.

Fig 2. The dependence of the height of the potential barrier of the temperature

Increasing the height of the potential barrier leads to increased electrical resistance of the GB, R<sub>2</sub>, Figure 1 wherein the total resistivity of the PS increases [1, 2]. In addition, (2) involves the  $J_{ss}$  - characteristic admittance traps, depending on their capture cross section, the energy distribution and position in space. To explain the inverse relationship between the currents and the admittances  $J_{ss}$  traps ( $Y_{ss}$ ), or the mechanism of CC transport along the GB, and use ris.1d equation for the current ( $J_{ss}$ ) arising in the process of capture and emission of CC in the traps, which we have proposed in [5].

On fig.1d shows a case where ohmic contacts C and D are located on opposite sides of the plates. In this case, the CC are not moving from one grain to another, they are captured by the traps and move on  $E_{ip}$  levels located at the GB, which gives rise observed in the current experiment,  $J_{ss}$ . Equivalent electrical circuit here consists of parallel-connected resistances grains  $(R_1)$  and GB  $(R_2)$ . Knowing that the conductivity of PS -  $(Y_{ss}(PS))$ , and grains -  $(Y_{ss}(R_1))$ , we can determine the conductivity of themselves GB  $(Y_{ss}(R_2))$ :

$$Y_{ss}(R_2) = Y_{ss}(PS) - Y_{ss}(R_1)$$

(3)

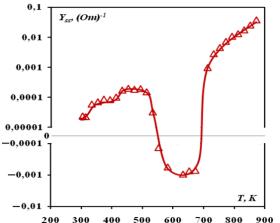

To calculate  $Y_{ss}(R2)$  use the results of the processing temperature dependences  $Y_{ss}(PS)$  and  $Y_{ss}(R1)$ , which are given by us in [3]. Figure 3 shows the temperature dependence of the conductivity of the GB, that is, admittance traps  $(Y_{ss}(R2))$  in GB.

International Journal of Advanced Research in Physical Science (IJARPS)

#### **Fig 3.** *dependence of admittance traps* $(Y_{ss})$ *in the grain boundaries of the temperature.*

It is seen that  $Y_{ss}(R2)$  changes with temperature is very complicated manner. For example, after a monotonic increase  $Y_{ss}(R2)$  in the range  $\sim 325 \div 343$ K, a sharp increase in this value, which corresponds to the average levels of traps  $E\approx 0,15$  eV and  $E\approx 0,17$  eV, as well as its sharp growth in the range of  $\sim 325 \div 343$  K, which corresponds to the level of expression of  $E\approx 0,36$  eV. Then there is a sharp drop and a change of direction  $Y_{ss}(R2)$ , that is The effect of temperature shift, which corresponds to the level of expression of  $E\approx 0,3$  eV. At higher temperatures, T $\geq 643$  K, there is a sharp increase and again a change of direction  $Y_{ss}(R2)$ . Absolute value  $Y_{ss}(R2)$  at the second switching in  $\sim 1000$  times greater than the first. The observed change  $Y_{ss}(R2)$  is correlated with the experimentally determined our data [1, 2], namely the fact that in this temperature range, there is such an abrupt change in the concentration and mobility of CC.

In the process of change in temperature is observed capture and emission of CC in the traps. In [5] to determine the direction of the current  $J_{ss}$  we have proposed the following conditions: the number of carrier capture more than their emission, the charge moves through the levels of traps along the border of the two contacting grains, which is accompanied by an increase in the total conductivity traps. This is the current direction  $J_{ss}$  we offer conditionally designate a "minus". If the issue prevails over the seizure, the charge moves in the opposite direction, and the direction of the current conditional  $J_{ss}$  can be denoted with a "plus". In the first case, the main CC move through the levels of traps along the border of the two contacting grains, in the second case they are moving in the opposite direction, but in both cases the conductivity increases traps. In our case, the geometrical parameter  $R_2$  for example, the length is ~2.10<sup>4</sup>nm, and its thickness is ~7 nm. It is evident that the geometrical parameters of  $R_2$  are in the nanometer range. From the results it follows that a handover or a change in the motion of CC occurs only in the GB, i.e. in a volume of nanometric dimensions. As already noted, the movement of CC in such amounts may be accompanied by quantum size effects, which may be illustrated as follows.

It is known, for example, the Seebeck effect, which consists in the appearance of an electromotive force in a closed circuit of two dissimilar materials if their places of contacts maintained at different temperatures. That is, if along such a heated semiconductor (Fig.4) there is a temperature gradient, as a result the heat input Q, the charge carriers at the hot end (D) acquire higher velocity energy than the cold (C).

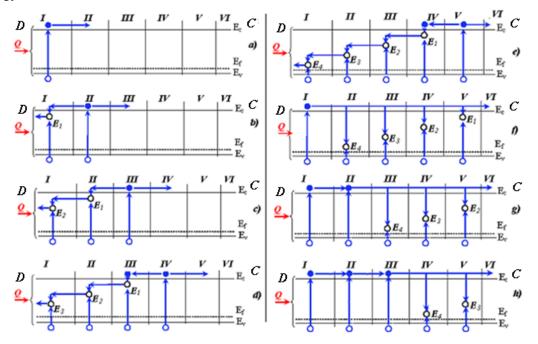

**Figure 4.** Band diagram of thermocouple based on semiconductors and the mechanism and process of carrier drift with rekombinatsonnyh centers.

In addition, in a semiconductor, including PS and, in a certain temperature range, the concentration of CC and hence their conductivity increases with increasing temperature. The

International Journal of Advanced Research in Physical Science (IJARPS)

# Some Features of the Transport of Charge Carriers in the Grain Boundaries of Polycrystalline Silicon

result is a flow of CC from the hot end (D) to a cold (C) (Figure 4), and in a closed circuit current occurs. 4 shows the band diagram of the area of the GB, which is a different resistance  $R_2$  or thermoelectric generators nanometric size. It can be divided into several sections, as shown in Figure 4. To estimate the flow or drift of the CC with RC, we use the results of [1, 2], ie, accept experimentally validated conditions for the appearance of RC at specific energy levels, for example, the energy level with E~0.15 eV appears at T2~50 °C, and at T3~70 °C this level disappears and shows a new level of E~0.17 eV, then this level, too, disappears, but it is accompanied by the manifestation of a new level with E~0.3 eV, which occurs when T4~100 °C.

When T5~250 °C and this level disappears, but it appears a new level of E~0.36 eV. In this, the system actually taking place, for example, fine-grained PS with normal for a sufficiently high concentration of deep energy levels caused as a residual deep impurities and unavoidable defects at the GB, changing the flow of CC occurs in the following sequence:

1 At the beginning of the heating process, for example, if the temperature of the section I is increased from room temperature to T1<50 °C, there is a flow of CC from the hot end (D) to a cold (C), going through all the successive portions, II, III, IV, V and VI (Figure 4), resulting in a closed circuit current occurs, in this case  $J_{ss}$  current.

2 With the increase of the heat input to the sample accompanied by an increase in temperature to a value T2, lying between 50 and 70°C at station I, and its increase in phase II from room temperature to T1 <50 °C, the section I expression observed RC E~0.15 eV. In this case, the thermal generated CC are captured at these levels. If the concentration of these levels would be higher than the concentration of CC at the site II, that the flow of CC will be directed from the Phase II area in the direction of I. That is, as a result of charge trapping at E~0.15 eV is happening on the heated section I (Fig.4b) actually changes the direction of the flow of CC from the end (C) to the end (D).

3 If the temperature of the section I is raised to a value T3 lying in the range from 70 °C to 100 °C, in phase II it is observed at temperature T2 lying in the range from 50 °C to 70 °C, and in the section III it will increase from room temperature to T1<50 °C, in the area I will be actively manifest RC with energy E~0.17 eV, and in the section II, respectively, the RC with E~0.15 eV and thermal generated CC will not be captured, at these sites, respectively, at the levels of E~0.17 eV and E~0.15 eV. If their concentration is higher than that of thermal generated CC at the site III, which is in this range of temperatures is so, then there will be a stream or a drift of CC in the direction of section I and section II, which illustrates (fig.4c). That is, the flow of CC will also be sent from the end (C) to the end (D).

4 When temperature at the sections I, II, and III, respectively, make the quantities: T4 of 100 °C to 250 °C; T3 from 70 °C to 100 °C; and T2 from 50 °C to 70 °C, and at these sites will be observed characteristic of these temperature ranges, the RC with energy levels E~0.3 eV and E~0.17 eV and E~0.15 eV, respectively, and the temperature of the portion IV increase from room temperature to T1<50 °C, flow or drift of CC (ris.1e, 1f, 1g and 1h), to move in the same direction as before from the end (C) the end (D). And all this process with less intensity will continue until the complete disappearance of the RC. In [1, 2] it is the effect of temperature variation RC for transport of CC in heating PS in the range from room temperature to 300 °C. We observed experimentally. Thus a sequential extinction RC, respectively, at sites I, II, III is a change of flow direction from the end of the CC (D) to the end (C).

Thus, the results obtained are in direct conflict with the established position, according to which the CC trapped at RC do not participate in the conduction. This, of course, there are no flow of CC, resulting in a closed circuit current cannot flow. However, our experimental results obtained on samples of fine-grained PS to indicate origin, and switching the current and voltage (thermo power) [9]. This means that in the process of interaction with the RC, characteristic of PS thermo-generated CC do not disappear, and are involved in the conduction of the proposed mechanism.

### REFERENCES

B.M. Abdurakhmanov, L.O. Olimov, and M.S. Saidov.Electrophysical Properties of Solar Polycrystalline Silicon and Its n+-p Structures at Elevated Temperatures. // Applied Solar Energy ISSN 0003-701X. 2008, vol. 44.№1, r.46 ÷ 52.

- [2] S. Zaynabidinov, R. Aliev, L.O. Olimov. High temperature features of the polycrystalline silicon physical properties. ISSN 0503-1265. Ukr.J.Phys. 2006, V.51.N 7.p. 699 ÷ 702.

- [3] L.O.Olimov, M. Muydinova, F.L.Omonboev. Electrical properties of grain boundaries in the bulk of the polycrystalline silicon. Physical-Surface Engineering, 2013, vol. 11, № 2, vol. 11, No. 2

- [4] The polycrystalline semiconductors. Physical properties and applications: Per. Translated from English. //Pod.red. Harbeck, the world.M., (1989) 344 p.

- [5] L.O. Olimov. Model of the Grain Boundary in pn Structures Based on Polycrystalline Semiconductors. // Applied Solar Energy ISSN 0003-701X. 2010, vol. 46. №2, r.118 ÷ 121.

- [6] B.M.Abdurakhmanov, L.O.Olimov. Detection of impurity voltaicheskih effects in singlecrystal silicon solar cells. Journal DAN Uzbekistan, 2009, №1, S.26-29.

- [7] L.O.Olimov. Influence of grain boundaries on the transport of charge carriers in polycrystalline silicon. Journal of Physics of Uzbekistan, 2005, №3, S.231-233.

- [8] L.O. Olimov1,\*,B.M. Abdurakhmanov. The Features of Impurity Thermal-Photovoltaic and thermal-Voltaic Effect of Polycrystalline Structures. Advances in Energy and Power 1(2): 51-55, 2013.

- [9] B.M.Abdurakhmanov, L.O.Olimov, ShKuchkanov.Switching currents and voltages at heating samples of polysiliconbesperehodnyh.Journal of the Academy of Sciences of Uzbekistan DAN. 2012. №3. S28-30.